Basic Processing Unit

Page Contents

Overview

- Instruction Set Processor (ISP)

- Central Processing Unit (CPU)

- A typical computing task consists of a series of steps specified by a sequence of machine instructions that constitute a program.

- An instruction is executed by carrying out a sequence of more rudimentary operations.

Fundamental Concepts

- The processor fetches one instruction at a time and performs the operation specified.

- Instructions are fetched from successive memory locations until a branch or a jump instruction is encountered.

- The processor keeps track of the address of the memory location containing the next instruction to be fetched using Program Counter (PC).

- Instruction Register (IR)

Executing an Instruction

- Fetch the contents of the memory location pointed to by the PC.

- The contents of this location are loaded into the IR (fetch phase).

- IR ← [[PC]]

- Assuming that the memory is byte addressable, increment the contents of the PC by 4 (fetch phase).

- PC ← [PC] + 4

- Carry out the actions specified by the instruction in the IR (execution phase).

Executing an Instruction

Transfer a word of data from one processor register to another or to the ALU.

Perform an arithmetic or a logic operation and store the result in a processor register.

Fetch the contents of a given memory location and load them into a processor register.

Store a word of data from a processor register into a given memory location.

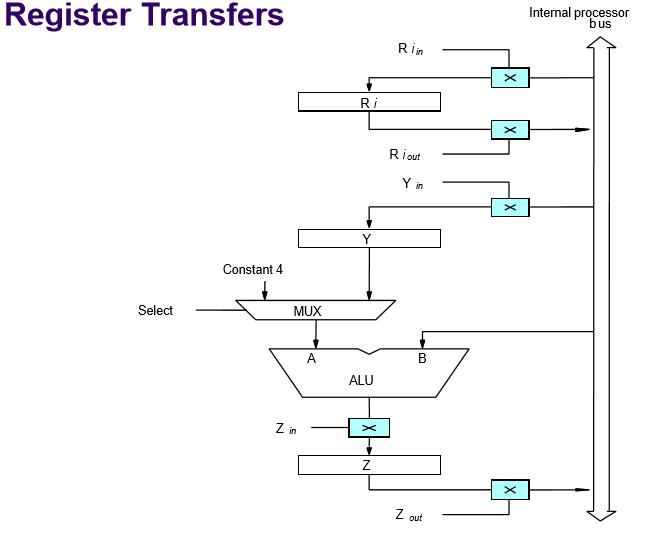

Register Transfers

All operations and data transfers are controlled by the processor clock

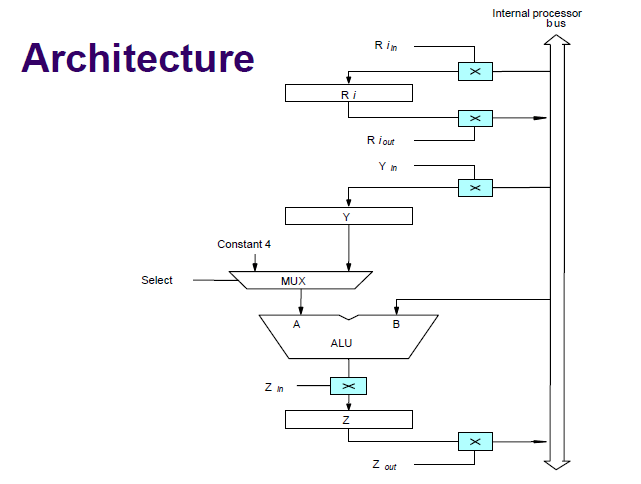

Performing an Arithmetic or Logic Operation

The ALU is a combinational circuit that has no internal storage.

- ALU gets the two operands from MUX and bus. The result is temporarily stored in register Z.

- What is the sequence of operations to add the contents of register R1 to those of R2 and store the result in R3?

- R1out, Yin

- R2out, SelectY, Add, Zin

- Zout, R3in

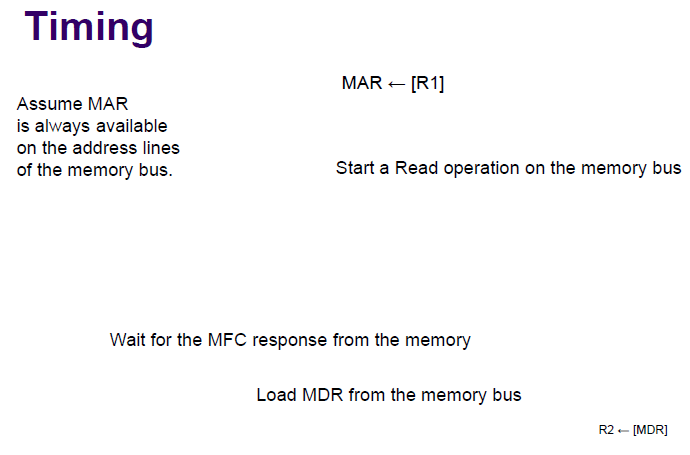

Fetching a Word from Memory

- Address into MAR; issue Read operation; data into MDR.

- The response time of each memory access varies (cache miss, memory-mapped I/O,…).

- To accommodate this, the processor waits until it receives an indication that the requested operation has been completed (Memory-Function-Completed, MFC).

- Move (R1), R2

- MAR ← [R1]

- Start a Read operation on the memory bus

- Wait for the MFC response from the memory

- Load MDR from

Signals activated

- R1out, MARin, Read

- MDRinE, WMFC

- MDRout, R2in

Basic Processing Unit

Timing of Basic Processing Unit

The figure represents Timing of a memory Read operation.

Assume MAR is always available on the address lines of the memory bus.

Also Read

Data Structures For Language Processing (System Programming/Search Organization/Hash Table/Heap)

Linkers, Loaders and Software

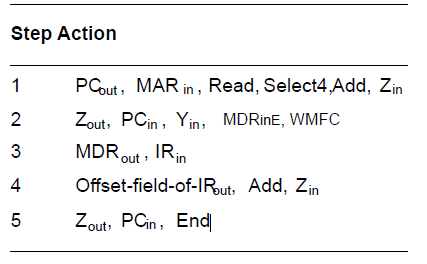

Execution of a Complete Instruction

- Add (R3), R1

- Fetch the instruction

- Fetch the first operand (the contents of the memory location pointed to by R3)

- Perform the addition

- Load the result into R1

Architecture of Basic Processing Unit

Execution of a Complete Instruction

- Add (R3), R1

- M DRinE, WMFC

Control Sequencer execution of the instruction Add (R3),R1.

Execution of Branch Instructions in Basic Processing Unit

- A branch instruction replaces the contents of PC with the branch target address, which is usually obtained by adding an offset X given in the branch instruction.

- The offset X is usually the difference between the branch target address and the address immediately following the branch instruction.

- Conditional branch

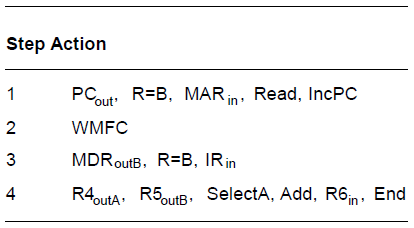

Multiple-Bus Organization

- Add R4, R5, R6

Also read